Dvoukan�lov� GENER�TOR harmonick�ho sign�lu na principu DDS, 40 MHz (moje bakal��sk� pr�ce)

www.elweb.cz

www.elweb.cz

Anotace

V pr�ci je pops�n n�vrh a realizace dvoukan�lov�ho gener�toru harmonick�ho sign�lu, jeho� j�drem je integrovan� obvod p��m� digit�ln� synt�zy. Gener�tor umo��uje prost�ednictv�m numerick� kl�vesnice a LCD displeje jednodu�e nastavovat amplitudu, vz�jemn� f�zov� posuv a frekvenci v�stupn�ch sign�l� v rozsahu 1 Hz a� 40 MHz.

Abstract

This project

describes a development and an execution of two-channel harmonic generator

which is based on an integrated circuit of a direct digital synthesis. The

generator allows setting output amplitude, phase shift and frequency in range

from 1 Hz up to 40 MHz by numeric keyboard easily.

Obsah

Pozn�mka: Chyby form�tov�n� vznikly p�i konverzi z origin�lu na dokument pro web a jejich oprava by byla p��li� zdlouhav�...1.������ P��m� digit�ln� synt�za

1.1.����� Blokov� sch�ma a popis funkce DDS

1.2.����� Ne��douc� spektr�ln� slo�ky v�stupn�ho sign�lu

2.2.����� Zp�soby realizace DDS

2.3.3.������ Vybran� parametry

2.4.����� Blokov� sch�ma gener�toru.

2.5.����� N�vrh - Analogov� ��st

2.5.2.������ Diferenci�ln� a v�stupn� zesilova�e

2.6.����� Sch�matick� n�vrh - Digit�ln� ��st

2.6.1.������ ��d�c� mikrokontrol�r

3.1.����� Desky plo�n�ch spoj�

3.2.����� Program mikrokontrol�ru

4.1.����� �rovn� v�stupn�ho v�konu harmonick�ch slo�ek

4.2.����� Vz�jemn� f�zov� posuv

Seznam p��loh

1) Seznam pou�it�ch sou��stek

2) Celkov� sch�ma gener�toru

Gener�tory pat�� mezi z�kladn� p��stroje pou��van� v m���c�ch laborato��ch, kde nach�zej� uplatn�n� p�edev��m jako zdroje testovac�ho sign�lu. M��eme je d�lit dle r�zn�ch krit�ri�. P�edev��m v�ak podle frekven�n�ho rozsahu v�stupn�ho sign�lu, jeho �asov�ho pr�b�hu nebo dle zp�sobu generov�n� sign�lu, respektive zp�sobu nastaven� a stabilizace v�stupn� frekvence a v�stupn�ho v�konu (amplitudy).

P��stroj, kter� jsem v r�mci t�to pr�ce navrhl a sestavil, spad� sv�m frekven�n�m rozsahem 1 Hz a� 40 MHz do kategorie n�zkofrekven�n�ch gener�tor�. Spodn� hranice vysokofrekven�n� techniky nen� p�esn� stanovena, ale m��eme ji popsat jako frekvenci nad n� nelze pou��vat k popisu obvod� soust�ed�n� parametry b�n� teorie obvod�. Maxim�ln� v�stupn� frekvence tohoto gener�toru ji� m��e b�t za ur�it�ch okolnost� nad touto pomyslnou hranic�.

P��stroj bude generovat dva nap�ov� re�ln� sign�ly se stejnou av�ak nastavitelnou frekvenc� a s harmonick�m pr�b�hem. Co� odpov�d� jedn� - v ide�ln�m p��pad� jedin�, v praxi v�ak jen v�razn� p�evl�daj�c� - spektr�ln� ���e ve frekven�n�m spektru v�stupn�ho sign�lu.

U ka�d�ho z t�chto dvou sign�l� bude mo�n� nastavit jejich amplitudu v rozsahu 0 V a� 2,55 V p�i zat�en� v�stup� impedanc� 50 Ω. Bude rovn� mo�n� nastavit vz�jemn� f�zov� posuv t�chto dvou sign�l� v pln�m rozsahu 0 a� 360� (2π).

Z hlediska frekven�n� stabilizace spad� p��stroj do kategorie tzv. syntez�tor�, kter� umo��uj� na rozd�l od voln� b��c�ch gener�tor� p�esn�j�� nastaven� a lep�� stabilitu v�stupn� frekvence.

Syntez�tory frekvence obecn� vyu��vaj� referen�n� sign�l s konstantn� frekvenc�. V�stupn� frekvence je pak pomoc� digit�ln�ch, digit�ln�-analogov�ch a/nebo analogov�ch obvod� generov�na jako ur�it� n�sobek (pod�l) t�to referen�n� frekvence a lze ji m�nit jen diskr�tn�. Referen�n� oscil�tor s pevnou v�stupn� frekvenc� lze v praxi vytvo�it s velmi dobrou frekven�n� stabilitou, respektive ��dov� lep�� ne� v p��pad� oscil�tor� s prom�nnou frekvenc�. Frekven�n� stabilita v�stupn�ho sign�lu je pak d�na pouze frekven�n� stabilitou referen�n�ho oscil�toru.

V p��pad� p��m� digit�ln� synt�zy je syntez�tor tvo�en v�hradn� digit�ln�mi obvody a v�stupn�m digit�ln�-analogov�m p�evodn�kem. P��m� digit�ln� synt�za je ozna�ov�na tak� zkratkou DDS z anglick�ho Direct Digital Synthesis.

Na obr. 1.1 je zn�zorn�no z�kladn� blokov� sch�ma p��m� digit�ln� synt�zy.

Obr. 1.1 : Blokov� sch�ma p��m� digit�ln� synt�zy

Bin�rn� ��slo ur�uj�c� v�stupn� frekvenci se vkl�d� s�riov� nebo paraleln� do tzv. delta registru. Toto ��slo je ur�eno dle konkr�tn� realizace 24 a� 48 bity a naz�v� se lad�c� slovo. V blokov�m sch�matu je ozna�eno jako M. Po resetu jsou oba registry vynulov�ny. P�i ka�d�m hodinov�m cyklu akumul�tor f�ze p�i�te k aktu�ln� hodnot� N ve f�zov�m registru hodnotu M z delta registru pomoc� s��ta�ky. Dokud nedojde k p�ete�en� f�zov�ho registru, bude platit pro k-t� hodinov� cyklus:

|

|

(1.1) |

Hodnota ve f�zov�m registru se tedy bude p�i konstantn� hodinov� frekvenci v �ase line�rn� zvy�ovat. K p�ete�en� f�zov�ho registru zde dojde ka�dou periodu v�stupn�ho sign�lu. P�i p�ete�en� ve f�zov�m registru z�stane zbytek po p�ete�en� a d�j d�le pokra�uje. F�zov� registr spolu se s��ta�kou tvo�� tzv. f�zov� akumul�tor. Hodnota f�zov�ho registru adresuje m�sto v pam�ti ROM s tabulkou funkce sinus. V t�to pam�ti jsou ulo�eny hodnoty funkce sinus pro diskr�tn� a line�rn� se zv�t�uj�c� argument (�hel). Aby nemusela b�t pam� ROM zbyte�n� velik�, pou��v� se pro jej� adresaci pouze n�kolik (b�n� 10 a� 14) nejvy���ch bit� z f�zov�ho akumul�toru.

Na obr. 1.2 je zobrazen digit�ln� f�zov� kruh zjednodu�en�ho DDS syst�mu pro maxim�ln� hodnotu� Nmax = 15 a pro lad�c� slovo M = 3. Po resetu je ve f�zov�m registru hodnota N = 0, co� odpov�d� bodu na kruhu zcela vpravo a nulov� hodnot� funkce sinus. P�i prvn�m hodinov�m cyklu se hodnota f�zov�ho registru zv��� na N = 3, co� odpov�d� skoku na digit�ln�m f�zov�m kruhu proti sm�ru hodinov�ch ru�i�ek. Na tomto kruhu je vyzna�ena i hodnota ulo�en� v ROM pam�ti funkce sinus jako svisl� ��ra mezi osou a konkr�tn�m bodem na kruhu.

Obr. 1.2 : Digit�ln� f�zov� kruh

Frekvence v�stupn�ho sign�lu bude:

|

|

(1.2) |

kde fs je hodinov� frekvence a fout je frekvence v�stupn�.

Maxim�ln� hodnota lad�c�ho slova vych�z� z Nyqustova krit�ria. Maxim�ln� hodnota p�i�ten� f�ze je tedy v tomto kruhov�m diagramu 180�, co� odpov�d� v tomto konkr�tn�m p��pad� Mmax = 8. P�i M = 8 by sice bylo spln�no Nyqustovo krit�rium, ale na v�stupu by mohl b�t obd�ln�kov� sign�l n�hodn� amplitudy a nebo dokonce konstantn� nulov� �rove�. Proto plat�:

|

|

(1.3) |

V praxi je v�ak t�eba volit maxim�ln� hodnotu lad�c�ho slova ni��� kv�li re�ln�m vlastnostem v�stupn�ho rekonstruk�n�ho filtru, respektive jeho omezen� strmosti.

Z toho pak vypl�v� maxim�ln� mo�n� v�stupn� frekvence:

|

|

(1.4) |

|

|

|

|

V praxi se v�ak pou��v� maxim�ln� t�etina nebo �tvrtina hodinov� frekvence kv�li ji� zm�n�n� omezen� strmosti rekonstruk�n�ho filtru. |

|

V�stupn� sign�l obvodu p��m� digit�ln� synt�zy obsahuje velik� mno�stv� (teoreticky nekone�n� mnoho) ne��douc�ch harmonick�ch slo�ek. Sign�l je vytv��en vzorkov�n�m D/A p�evodn�kem, a proto bude ob�lku vznikl�ch spektr�ln�ch slo�ek tvo�it funkce sin(x)/x. Krom� t�chto spektr�ln�ch �ar se ve spektru v�stupn�ho sign�lu objev� mno�stv� vy���ch harmonick�ch slo�ek od generovan� frekvence, kter� vznikaj� p�edev��m z d�vodu nelinearity D/A p�evodn�ku. V�echny vy��� harmonick� slo�ky s frekvenc� vy��� ne� je polovina frekvence vzorkovac� se objev� jako p�enesen� obraz v z�kladn�m p�smu. V�e je patrn� z obr. 1.3, na kter�m je zjednodu�en� zobrazen p��klad spektra v�stupn�ho sign�lu p�i vzorkovac� frekvenci 100 MHz a generovan� frekvenci 30 MHz.

Obr. 1.3 : P��klad spektra v�stupn�ho sign�lu

P�enesen� vy��� harmonick� do z�kladn�ho p�sma nelze potla�it v�stupn�m filtrem (typu doln� propust).

Podrobn�ji je princip p��m� digit�ln� synt�zy pops�n nap��klad v (1).

P�ed zah�jen�m vlastn�ho n�vrhu gener�toru jsem nejprve konkretizoval a up�esnil n�sleduj�c� po�adavky, respektive c�le, kter�ch bych v r�mci t�to pr�ce cht�l dos�hnout nad r�mec zad�n� pr�ce.

� Dva v�stupy

� Mo�nost regulace:

o v�stupn� frekvence (1 Hz a� 40 MHz)

o vz�jemn�ho f�zov�ho posuvu (0� a� 360�)

o amplitudy v�stupn�ho nap�t� pro oba kan�ly samostatn� (0 V a� 2,55 V)

� Ovl�d�n� p��stroje prost�ednictv�m numerick� kl�vesnice

� Zobrazen� aktu�ln�ch informac� na LCD displeji

� Odstup ne��douc�ch harmonick�ch slo�ek v�stupn�ho sign�lu 60 dB

� Realizace v podob� plnohodnotn�ho p��stroje

Obvod p��m� digit�ln� synt�zy lze realizovat n�kolika zp�soby. Volil jsem mezi n�sleduj�c�mi t�emi mo�nostmi:

1) programov� �e�en� ( mikrokontrol�r a D/A p�evodn�k )

2) pevn� logika ( hradlov� pole a D/A p�evodn�k )

3) integrovan� obvod p��m� digit�ln� synt�zy

Realizace s mikrokontrol�rem nar�� na po�adovanou v�stupn� frekvenci, p�i kter� by musela b�t taktovac� frekvence mikrokontrol�ru p��li� vysok�. Pou�it� pevn� logiky by sice umo�nilo vy��� pracovn� kmito�et, ale jej� n�vrh by byl p��li� komplikovan�. Proto jsem se rozhodl pro pou�it� integrovan�ho obvodu DDS.

Na z�klad� pr�zkumu trhu jsem zjistil, �e nejv�t�� sortiment takov�chto obvod� nab�z� firma Analog Devices. A po prostudov�n� n�kolika katalogov�ch list� a konzultaci se zastoupen�m zm�n�n�ho v�robce se mi jako optim�ln� jev� integrovan� obvod AD9958, kter� obsahuje dva obvody DDS se spole�n�m, synchronn�m vstupem hodinov�ch impulz�.

www.elweb.cz

Integrovan� obvod AD9958 firmy Analog Devices (2) obsahuje dv� j�dra DDS, kter� umo��uj� nez�visl� nastaven� frekvence, f�zov�ho posuvu a amplitudy pro oba kan�ly. ��d�c� obvody obou kan�l� jsou taktov�ny shodn�m zdrojem hodinov� frekvence a jsou tedy vz�jemn� synchronn�. Pr�v� proto je AD9958 vhodn� pro tuto aplikaci.

www.elweb.cz

2.3.1. Vlastnosti

� 2 synchronn� DDS j�dra

� nez�visl� nastaven� frekvence, f�ze a amplitudy obou kan�l�

� p�izp�soben� zpo�d�n� zm�n parametr� v�stupn�ch sign�l�

� line�rn� rozm�t�n� frekvence, f�ze i amplitudy

� a� �estn�cti-�rov�ov� diskr�tn� modulace frekvence, f�ze i amplitudy

� s�riov� ��zen� po SPI sb�rnici

� dvojit� nap�jec� nap�t� 1,8 V a 3,3 V

� mo�nost synchronizace v�ce integrovan�ch obvod�

� integrovan� n�sobi�ka vstupn� hodinov� frekvence (4x a� 20x)

www.elweb.cz

� pouzdro 56-Lead LFCSP

V n�sleduj�c� tab. 2.1 jsou uvedeny po�ty bit� jednotliv�ch ��st� integrovan�ho obvodu AD9958.

www.elweb.cz

Tab. 2.1 : Po�ty bit� ��st� AD9958

|

|

po�et bit� |

|

v�stupn� D/A p�evodn�ky |

10 |

|

nastaven� frekvence |

32 |

|

nastaven� f�ze |

14 |

|

nastaven� amplitudy |

10 |

www.elweb.cz

2.3.2. Blokov� sch�ma

Na obr. 2.1 je uvedeno vnit�n� blokov� sch�ma integrovan�ho obvodu AD9958 p�evzat� z (2). Jsou zde vid�t ob� j�dra p��m� digit�ln� synt�zy (DDS Core), ��zen� v�stupn� amplitudy (AMP), integrovan� digit�ln�-analogov� p�evodn�ky (DAC) a ��d�c� logika (Timing and control logic). D�le se v AD9958 nach�z� obvody pro generov�n� a �pravu hodinov�ho sign�lu v�etn� n�sobi�ky frekvence (REF clock multiplier) a obvody pro s�riovou komunikaci.

www.elweb.cz

Obr. 2.1 : Blokov� sch�ma AD9958

2.3.3. Vybran� parametry

www.elweb.cz

|

parametr |

hodnota |

|

Maxim�ln� hodinov� frekvence |

500 MHz |

|

Maxim�ln� v�stupn� proud D/A p�evodn�k� |

10 mA |

|

Maxim�ln� chyba zes�len� |

�10 % |

|

Maxim�ln� nelinearita |

�1 LSB |

|

Odd�len� kan�l� |

72 dB |

www.elweb.cz

www.elweb.cz

N�sleduj�c� obr�zek obr. 2.2 zobrazuje blokov� sch�ma cel�ho p��stroje tak, jak jsem jej navrhl. P��stroj jsem rozd�lil na dv� samostatn� ��sti � digit�ln� (horn� ��st blokov�ho sch�matu) a analogovou (spodn� ��st). Tyto dv� ��sti bude mo�no navrhovat, sestavovat a testovat samostatn�, co� zjednodu�� celkovou realizaci. Digit�ln� ��st slou�� k ��zen� integrovan�ho obvodu AD9958 a tak� pro komunikaci s u�ivatelem. Tato ��st je tvo�ena mikrokontrol�rem, ke kter�mu je p�ipojen textov� LCD displej 2x 16 znak�, Bluetooth modul pro bezdr�tov� ovl�d�n� a tak� maticov� numerick� kl�vesnice se �estn�cti tla��tky pro ovl�d�n� p��stroje.

Obr. 2.2 : Blokov� sch�ma

www.elweb.cz

Analogovou ��st tvo�� p�edev��m integrovan� obvod p��m� digit�ln� synt�zy AD9958. Jeho hodinov� frekvence je vytv��ena extern�m gener�torem. Vstupy modulace jsou opat�eny vstupn�mi p�ep�ov�mi ochranami a vstupn�mi zesilova�i. V�stupy AD9958 jsou komplement�rn� a vysoko-impedan�n�. Pro jejich impedan�n� p�izp�soben� na 50 Ω a zm�nu na jednoduch� (nesymetrick�) v�stupy jsou pou�ity diferenci�ln� zesilova�e. Za nimi pak n�sleduj� rekonstruk�n� pasivn� LC filtry typu doln� propust. Tyto filtry jsou rovn� impedan�n� p�izp�sobeny na 50 Ω. Nakonec je sign�l nap�ov� i proudov� zes�len v�stupn�mi zesilova�i a op�t p�izp�soben v�stupn�mi odpory op�t na 50 Ω.

Jednotliv� ��sti blokov�ho sch�matu budou podrobn�ji pops�ny d�le.

Celkov� sch�ma p��stroje je uvedeno v p��loze.

www.elweb.cz

2.5.1. DDS

2.5.1.1. Zapojen� AD9958

Integrovan� obvod AD9958 m� 56, respektive s chlad�c� plo�kou 57 v�vod�. V�t�ina z nich je vyu�ita pro p�ipojen� nap�jec�ho nap�t� nebo zem. N�sleduj�c� tab. 2.2 je p�evzata z (2) a zobrazuje popis v�ech pin�. Po prostudov�n� jednotliv�ch ��st� katalogov�ho listu jsem ji doplnil o konkr�tn� vyu�it� (zapojen�) jednotliv�ch pin� v t�to aplikaci.

Tab. 2.2 : Popis funkce a zapojen� pin� AD9958

|

��slo pinu |

n�zev pinu |

I/O |

popis funkce pinu |

zapojen� |

|

1 |

SYNC_IN |

I |

Synchronizace v�ce obvod�

AD9958 |

GND |

|

2 |

SYNC_OUT |

O |

Synchronizace v�ce obvod�

AD9958 |

- |

|

3 |

MASTER_RESET |

I |

Reset |

PIC I/O |

|

4 |

PWR_DWN_CTL |

I |

Extern� vypnut� |

GND |

|

5, 7, 11, 15, 19, 21, 26,

29, |

AVDD |

I |

Nap�jec� nap�t� analogov�

��sti (1,8V) |

analog. +1,8V |

|

�30, 31, 33, 35, 36, 37, 39 |

|

|

|

|

|

6, 10, 12, 16, 18, 20, 25 |

AGND |

I |

Zem analogov� ��sti |

GND |

|

45, 55 |

DVDD |

I |

Nap�jec� nap�t� digit�ln�

�asti (1,8V) |

dig. +1,8V |

|

44, 56 |

DGND |

I |

Zem digit�ln� ��sti |

GND |

|

8 |

CH0_IOUT |

O |

V�stup DA p�evodn�ku |

1. v�stup |

|

9 |

CH0_IOUT |

O |

Komplement�rn� v�stup DA

p�evodn�ku |

1. v�stup kompl. |

|

13 |

CH1_IOUT |

O |

V�stup DA p�evodn�ku |

2. v�stup |

|

14 |

CH1_IOUT |

O |

Komplement�rn� v�stup DA

p�evodn�ku |

2. v�stup kompl. |

|

17 |

DAC_RSET |

I |

Referen�n� proud pro oba DA

p�evodn�ky |

R 4,7 kΩ na GND |

|

22 |

REF_CLK |

I |

Komplement�rn� vstup hodinov�ho

sign�lu |

C 100 nF na GND |

|

23 |

REF_CLK |

I |

Vstup hodinov�ho sign�lu |

hodinov� sign�l |

|

24 |

CLK_MODE_SEL |

I |

��d�c� vstup nastavuj�c� typ

oscil�toru |

GND |

|

27 |

LOOP_FILTER |

I |

Extern� kompenzace PLL

filtru |

C 680pF na GND |

|

28, 32, 34, 38 |

NC |

- |

Bez vnit�n�ho zapojen� |

- |

|

40, 41,42,43 |

P0, P1, P2, P3 |

I |

Datov� vstupy |

dig.vstupy |

|

46 |

I/O_UPDATE |

I |

P�esun dat ze vstup� do

vstupn�ch registr� |

PIC I/O |

|

47 |

CS |

I |

V�b�r z v�ce obvod� na

spole�n� SPI sb�rnici |

PIC I/O |

|

48 |

SCLK |

I |

Hodinov� sign�l s�riov�

komunikace |

PIC I/O |

|

49 |

DVDD_I/O |

I |

Nap�jec� nap�t� digit�ln�

��sti (3,3V) |

dig. 3,3V |

|

50 |

SDIO_0, |

I/O |

Datov� port s�riov�

komunikace |

PIC I/O |

|

51 52, 53 |

SDIO_1:3 |

I/O |

Digit�ln� porty |

1: PIC I/O; 3:GND |

|

54 |

SYNC_CLK |

O |

�tvrtinov� frekvence

hodinov�ho sign�lu |

- |

Sch�ma ��sti zapojen� integrovan�ho obvodu AD9958 je zobrazeno na obr. 2.3. V lev� ��sti sch�matu je vid�t gener�tor hodinov� frekvence (viz d�le). Rezistory R5 a R6 p�izp�sobuj� logick� �rovn� pro komplement�rn� vstup extern�ho hodinov�ho sign�lu AD9958, kter� je odd�len keramick�m kondenz�torem C1. Druh� hodinov� vstup je p�ipojen p�es keramick� kondenz�tor C2 na zem. S�riov� kombinace kondenz�toru C3 a R7 slou�� jako extern� kompenzace vnit�n�ho PLL filtru. Rezistor R9 nastavuje maxim�ln� proud D/A p�evodn�k�. Rezistory R101, R102, R201 a R202 zat�uj� proudov� v�stupy D/A p�evodn�k�. V�echny ostatn� rezistory uveden� v tomto sch�matu slou�� pro p�izp�soben� logick�ch �rovn�.

Obr. 2.3 : Sch�ma ��sti zapojen� integrovan�ho obvodu AD9958

2.5.1.2. Synchronizace v�ce AD9958

V t�to aplikaci bude vyu��v�n pouze jeden integrovan� obvod AD9958, a proto nebude synchronizace vyu�ita. Z toho vypl�v� p�ipojen� synchroniza�n�ho vstupu SYNC_IN na zem a ponech�n� synchroniza�n�ho v�stupu SYNC_OUT bez elektrick�ho zapojen�.

www.elweb.cz

2.5.1.3. Zap�n�n�, reset

Integrovan� obvod AD9958 bude po zapnut� p��stroje st�le v zapnut�m re�imu. Vzhledem k nap�jen� p��stroje ze s�ov�ho adapt�ru nen� nutn� zab�vat se p��li� minimalizac� proudov�ho odb�ru. Z toho vypl�v� p�ipojen� ��d�c�ho vstupu PWR_DWN_CTL na zem. Vstup MASTER_RESET je p�ipojen na v�stup mikrokontrol�ru a umo��uje tak programov� restartovat DDS. T�m se nastav� ve�ker� vnit�n� registry na v�choz� hodnoty.

2.5.1.4. Hodinov� sign�l

www.elweb.cz

Vzhledem k principu regulace v�stupn� frekvence v obvodu p��m� digit�ln� synt�zy, uleh�� n�vrh volba frekvence hodinov�ho sign�lu jako cel� mocnina dvou (Hz). To umo�n� snaz�� ��zen� a zjednodu�en� programu mikrokontrol�ru. V�stupn� frekvence v Hz pak bude p��mo odpov�dat bin�rn�mu ��slu ur�en�ho ��st� frekven�n�ho registru. Klasick� krystaly se s takovouto hodnotou frekvence bohu�el b�n� nevyr�b�j�. Z tohoto d�vodu jsem jako zdroj hodinov� frekvence pou�il programovateln� krystalov� oscil�tor firmy Epson, konkr�tn� typ SG8002.

Oscil�tory �ady SG8002 obsahuj� krystal, programovatelnou d�li�ku kmito�tu, f�zov� z�v�s PLL a pam� PROM. Sou�asn� je integrov�n programovatel� v�stupn� obvod, kter� umo��uje zat�it v�stup obvody CMOS nebo TTL.

Parametry SG8002JC:

- nap�jec� nap�t�: ������� ����������������������� 2,7 � 5 V

- frekven�n� stabilita �������������� ����������� � 50 ppm

Frekvence hodinov�ho sign�lu by m�la b�t s rezervou vy��� ne� dvojn�sobek maxim�ln� nastaviteln� v�stupn� frekvence. ��m v�t�� bude tato rezerva, respektive ��m bude v�t�� frekven�n� odstup v�stupn� frekvence od ne��douc�ch obraz� ve v�stupn�m frekven�n�m spektru, t�m budou kladeny men�� n�roky na strmost a tedy i slo�itost v�stupn�ho filtru.

Integrovan� obvod AD9958 dok�e pracovat s maxim�ln� hodinovou frekvenc� 500 MHz. Obsahuje rovn� programovatelnou n�sobi�ku vstupn� hodinov� frekvence. N�sobi�ku lze nastavit tak, aby n�sobila vstupn� frekvenci cel�m ��slem v rozsahu 4 � 20. S ohledem na v��e uveden� po�adavky a mo�nosti jsem se rozhodl pro pou�it� programovateln�ho oscil�toru SG8002 s naprogramovanou v�stupn� frekvenc� 224 Hz, tedy 16 777 216 Hz a nastaven� n�sobi�ky na 23, tedy 8-kr�t.

V�sledn� vnit�n� hodinov� frekvence obvodu AD9958 bude pak:

|

|

(2.1) |

Maxim�ln� v�stupn� frekvence je teoreticky dle vztahu (1.4):

|

|

(2.2) |

|

|

|

Vzhledem k omezen� strmosti v�stupn�ho rekonstruk�n�ho filtru bude maxim�ln� v�stupn� frekvence ni���, konkr�tn� 40 MHz.

Nejmen�� mo�n� lad�c� krok (nejmen�� mo�n� zm�na) v�stupn� frekvence AD9958 �je:

|

|

(2.3) |

|

Krok nastaven� v�stupn� frekvence gener�toru bude 1 Hz. Posledn�ch p�t bit� vkl�dan�ch mikrokontrol�rem do delta registru bude tedy v�dy nevyu�ito (budou zde v�dy nuly). |

|

2.5.1.5. V�stupy

Oba kan�ly integrovan�ho obvodu AD9958 maj� komplement�rn� proudov� v�stup D/A p�evodn�k�. Dle katalogov�ho listu maj� b�t tyto proudov� v�stupy (na rozd�l od v�t�iny ostatn�ch DDS obvod�) zakon�eny p�es prim�rn� vinut� VF transform�toru nebo p�es rezistory do nap�jec�ho nap�t� analogov� ��sti (+1,8 V). Vzhledem k po�adovan� regulaci v�stupn� frekvence v rozsahu mnoha ��d� by nebylo pou�it� VF transform�toru vhodn�. Z tohoto d�vodu jsem zvolil variantu zakon�en� proudov�ch v�stup� rezistory. P�i ur�en� jejich hodnoty jsem vych�zel z n�sleduj�c�ch informac� uveden�ch v katalogov�m listu.

- Maxim�ln� proud z jednoho v�stupu je limitov�n hodnotou 15 mA.

- P�i v�stupn�m proudu 15 mA v�ak doch�z� k ne��douc�mu zkreslen� a je vhodn� nep�esahovat hodnotu 10 mA.

- Nap�t� na v�stupech se m��e pohybovat maxim�ln� v intervalu < UAVDD � UOUT_MAX ; UAVDD + UOUT_MAX >, kde UOUT_MAX = 0,5 V. (Zde je vhodn� dodr�et rezervu nap��klad 20 %.)

- Maxim�ln� rozsah v�stupn�ho proudu lze nastavit volbou hodnoty rezistoru RSET .

V�stupn� proud jsem zvolil:

|

|

(2.4) |

Dle vzorce z katalogov�ho listu pak:

|

|

(2.5) |

Po zaokrouhlen� na nejbli��� hodnotu v �ad� E12:

|

|

(2.6) |

V�po�et hodnot zakon�ovac�ch rezistor� RTRM :

|

|

(2.7) |

Maxim�ln� amplituda na v�stupech AD9958 bude tedy UmmAD = 0,8 ∙ 0,5 = 0,4 V.

2.5.1.6. Komunikace s mikrokontrol�rem

Mikrokontrol�r ��d� obvod p��m� digit�ln� synt�zy prost�ednictv�m 4-vodi�ov� s�riov� sb�rnice. Pin SCLK nese hodinov� sign�l s�riov� komunikace, kter� je generov�n ��d�c�m mikrokontrol�rem. Pin SDIO_0 je vyu�it pro vlastn� s�riov� data. Po p�enosu s�riov�ch dat (instrukc� a/nebo hodnot) do AD9958 je vysl�n potvrzovac� impulz. K tomu slou�� pin IO_UPDATE. D�ky tomuto potvrzovac�mu impulzu jsou vnit�n� registry v AD9958 zm�n�ny ve stejn� okam�ik a nep�episuj� se v pr�b�hu p�enosu. Pin CS slou�� k zah�jen� a ukon�en� p�enosu. Rovn� by umo��oval v�b�r jednoho z AD9958, pokud by jich bylo na s�riov� sb�rnici p�ipojeno v�ce.

D�le jsou k mikrokontrol�ru p�ipojeny vstupy MASTER_RESET a SDIO_1. Pinem SDIO_1 jsou ovl�d�ny funkce souvisej�c� s line�rn�m rozm�t�n�m. (Line�rn� rozm�t�n� p�esahuje rozsah t�to pr�ce, ale je po��t�no s jeho mo�nou budouc� programovou implementac�.)

2.5.1.7. P�izp�soben� logick�ch �rovn�

Pou�it� mikrokontrol�r PIC16F877 a rovn� i programovateln� oscil�tor SG8002JC jsou nap�jeny nap�jec�m nap�t�m o hodnot� 5 V a jejich v�stupn� logick� �rovn� odpov�daj� logick�m �rovn�m obvod� TTL. P�i logick� jedni�ce maj� na v�stupu tedy t�m�� 5 V. Digit�ln� ��st obvodu AD9958 je v�ak nap�jena nap�t�m 3,3 V. Proto je pot�eba logick� �rovn� p�izp�sobit. Vzhledem k jednostrann� komunikaci jsem pou�il pro toto p�izp�soben� odporov� d�li�e nap�t� � viz obr. 2.4. P��padn� obousm�rn� komunikace by byla tak� mo�n�, proto�e pro zaji�t�n� logick� jedni�ky na vstupu mikrokontrol�ru sta�� nap�t� o hodnot� 2,4 V.

Obr. 2.4 : P�izp�soben� logick�ch �rovn� odporov�m d�li�em nap�t�

Hodnoty odpor� jednotliv�ch rezistor� odporov�ho d�li�e nap�t� by nem�ly b�t p��li� n�zk�, aby nedoch�zelo k proudov�mu p�et�en� v�stup� mikrokontrol�ru (p��padn� AD9958). Rovn� nesm� b�t p��li� vysok�, proto�e komunikace prob�h� na relativn� vysok�ch frekvenc�ch. Rozumn�m kompromisem jsou hodnoty v ��dech stovek Ω a� jednotek kΩ.

Hodnotu odporu rezistoru R1 jsem zvolil: R1 = 1,2 kΩ.

Hodnotu odporu rezistoru R2 jsem pak spo�etl n�sledovn�:

����������������������� �����������������������

|

|

(2.8) |

Z toho pak:

|

|

(2.9) |

Z �ady E24 jsem pak vybral hodnotu R2 = 2,2 kΩ.

2.5.2. Diferenci�ln� a v�stupn� zesilova�e

Vzhledem k tomu, �e jsou v�stupy proudov� a maj� �stit do nap�jec�ho nap�t� +1,8 V, lze na nich pouze sledovat nap�t�, ale nelze je proudov� d�le p��li� zat�it. Z v�stup� je pot�eba tak� odd�lit stejnosm�rnou slo�ku. Oba tyto po�adavky spl�uje zapojen� diferenci�ln�ho zesilova�e s opera�n�m zesilova�em. Sch�ma diferenci�ln�ho zesilova�e je uvedeno na obr. 2.5.

Obr. 2.5 : Diferenci�ln� zesilova�

Neinvertuj�c� vstupy diferenci�ln�ch zesilova�� ozna�en� jako UIN+ budou p�ipojeny k v�stup�m AD9958 a invertuj�c� vstupy ozna�en� jako UIN- budou p�ipojeny ke komplement�rn�m v�stup�m AD9958. Pro stejn� zes�len� sign�l� na neinvertuj�c�m i invertuj�c�m vstupu budou m�t rezistory R103 a R104 shodnou hodnotu odporu (R103 = R104). To sam� plat� i pro odpory dvojice rezistor� R105 = R106.

Zes�len� A1 diferenci�ln�ho zesilova�e je d�no pom�rem odpor� rezistor� R106/R104, respektive R105/R103 dle n�sleduj�c�ho vztahu:

|

|

(2.10) |

�����������

V�choz� odpor rezistoru R103, respektive R104 by m�l b�t dostate�n� velk�, aby nebyly proudov� v�stupy AD9958 p��li� zat�eny, ale z�rove� dostate�n� mal�, aby se p��li� neprojevily parazitn� kapacity, kter� by p�i v�stupn�ch frekvenc�ch v ��dech des�tek MHz mohly zp�sobit necht�n� �tlum sign�lu. Jako kompromis jsem zvolil hodnotu R103 = R104 = 1,2 kΩ.

Celkov� zes�len� diferenci�ln�ch a v�stupn�ch zesilova�� by m�lo b�t takov�, aby byla maxim�ln� amplituda v�stupn�ch sign�l� UmmOUT rovna 2,55 V p�i z�t�i 50 Ω, respektive 10,2 V �pi�ka-�pi�ka bez z�t�e.

Jak ji� bylo uvedeno v��e, maxim�ln� amplituda na v�stupech AD9958 UmmAD bude 0,4 V. Celkov� zes�len� bude tedy:

|

|

(2.11) |

�����������������������

Na pom�ru zes�len� diferenc��ln�ch zesilova�� A1 a v�stupn�ch zesilova�� A2 by v ide�ln�m p��pad� nez�le�elo, ale re�ln� opera�n� zesilova�e maj� r�zn� vlastnosti p�i r�zn�m v�sledn�m zes�len�. Z tohoto d�vodu by m�la b�t zes�len� A1 a A2 p�ibli�n� stejn�. Pou�it� opera�n� zesilova�e (viz d�le) maj� nejlep�� vlastnosti p�ibli�n� v rozsahu v�sledn�ch zes�len� 2 � 3. Pro p�esn� stejn� zes�len� (A1 = A2) plat�:

|

|

(2.12) |

Z toho pak:

|

|

(2.13) |

Nejbli��� hodnota v b�n� dostupn� �ad� E24 je 3 kΩ.

2.5.2.1. V�stupn� zesilova�e

V�stupn� zesilova�e slou�� k nap�ov�mu i proudov�mu zes�len� v�stupn�ho sign�lu za v�stupn�mi LC filtry. Jedn� se o opera�n� zesilova�e v neinvertuj�c�m zapojen�. Jeden z t�chto zesilova�� je uveden na obr. 2.6. Zes�len� v�stupn�ch zesilova�� je dle rovnice (2.12) A2 = 2,525. Odpor rezistoru R109 jsem zvolil: R109 = 1,2 kΩ. Z toho pak:

|

|

(2.14) |

Nejbli��� hodnota v �ad� je: R110 = 1,8 kΩ.

Rezistor R108 slou�� jako symetrick� zakon�en� v�stupn�ho LC filtru (viz d�le) R108 = 50 Ω.

Rezistor R111 p�izp�sobuje v�stup na 50 Ω. R111 = 50 Ω.

Obr. 2.6 : V�stupn� zesilova�

Maxim�ln� nastaviteln� v�stupn� frekvence se bude pohybovat v ��dech des�tek MHz, v�stupn� amplituda v ��dech jednotek volt� a v�stupn� proudy p�i impedan�n�m p�izp�soben� na 50 ٠budou dosahovat hodnot des�tek mA. Z t�chto d�vod� je nutn� volit speci�ln� opera�n� zesilova�e. Sv�mi parametry vyhovuj� nap��klad opera�n� zesilova�e ur�en� pro xDSL technologie. Z nep��li� velik�ho v�b�ru takov�chto opera�n�ch zesilova�� jsem dle parametrick�ch tabulek a katalogov�ch list� vybral integrovan� obvod THS3091 od Texas Instruments.

2.5.2.2. Vlastnosti THS3091

Vlastnosti obvodu THS3091 jsou p�evzaty z katalogov�ho listu (3).

- N�zk� zkreslen�

o druh� harmonick� slo�ka � 66 dBc (p�i 10 MHz a z�t�i 100 Ω)

o t�et� harmonick� slo�ka � 74 dBc (p�i 10 MHz a z�t�i 100 Ω)

- N�zk� �um

o neinvertuj�c� proudov� �um:� 14 pA.Hz-1/2

o invertuj�c� proudov� �um:����� 17 pA.Hz-1/2

o nap�ov� �um:���������������������� 2 nV.Hz-1/2

- ���ka p�sma�������������������������� 210 MHz (p�i zes�len� A = 2 a z�t�i RL = 100 Ω)

- Rychlost p�eb�hu������������������������������ 7300 V.�s-1

- Rozsah �nap�jec�ho nap�t� ��� ����������� �5 V � �15 V

2.5.3. V�stupn� filtry

2.5.3.1. Aktivn� nebo pasivn� ?

Nejprve jsem zva�oval pou�it� aktivn�ch filtr�. Respektive jsem hledal d�vod, pro� by aktivn� filtry nebylo mo�n� pou��t, a pro� se ve spojen� s p��mou digit�ln� synt�zou ani b�n� nepou��vaj�. Odpov�� na tuto ot�zku je nap��klad v (4). Zde je uv�d�na dosavadn� praktick� hranice mezn� frekvence ARC filtru p�ibli�n� 50 MHz. P�e se zde v�ak tak�, �e p�i mezn�ch kmito�tech nad 1 MHz vznikaj� zna�n� probl�my s projevy re�ln�ch vlastnost� pou�it�ch sou��stek. Tyto probl�my pr� nast�vaj� i p�i pou�it� modern�ch opera�n�ch zesilova�� s tranzitn�mi kmito�ty v ��du stovek MHz. Mezn� kmito�et zde pou�it�ho filtru by m�l b�t 40 MHz. Proto bude vhodn�j�� volit pasivn� LC filtry.

2.5.3.2. Po�adavky

V�stupn� filtry slou�� pro filtraci ne��douc�ch harmonick�ch slo�ek ve v�sledn�m v�stupn�m sign�lu obvodu p��m� digit�ln� synt�zy. P�i nastaven� v�stupn� frekvence na maxim�ln� hodnotu fout = 40 MHz se ve frekven�n�m spektru v�stupn�ho sign�lu objev� nejbli��� obraz (ne��douc� harmonick� slo�ka) na frekvenci:

|

|

(2.15) |

�Filtry musej� m�t p�edev��m dostate�nou strmost, aby dostate�n� potla�ily tento ne��douc� obraz. Vzhledem k parametr�m ostatn�ch sou��stek (p�edev��m opera�n�ch zesilova�� a obvodu p��m� digit�ln� synt�zy) lze pova�ovat za minim�ln� dostate�n� �tlum hodnotu 60 dB. V propustn�m p�smu by m�lo b�t v ide�ln�m p��pad� nulov� zvln�n� p�enosov� funkce, respektive nulov� �tlum. Pro n�vrh filtru jsem zvolil maxim�ln� �tlum v propustn�m p�smu 0,1 dB.

Gener�tor bude m�t dva v�stupy s nastaviteln�m vz�jemn�m f�zov�m posuvem. V ide�ln�m p��pad� by filtry tedy m�ly m�t nulov� f�zov� posuv. To je v praxi samoz�ejm� nemo�n�. Zde v�ak z�le�� jen na relativn�m f�zov�m posuvu mezi dv�ma v�stupn�mi sign�ly, nikoli na absolutn�m. Bude tedy sta�it, kdy� budou m�t oba filtry stejn� pr�b�h f�zov�ho posuvu v z�vislosti na frekvenci. To je ov�em tak� prakticky nemo�n� kv�li rozptylu hodnot pou�it�ch sou��stek, respektive jejich toleranci.

Typ filtr� jsem vyb�ral s ohledem na jejich slo�itost p�i spln�n� po�adovan� strmosti dan� v��e uveden�mi po�adavky a s ohledem na jejich citlivost zm�ny f�zov�ho posuvu p�i zm�n� hodnot pou�it�ch sou��stek. V aplika�n�ch pozn�mk�ch firmy Analog Devices (5) doporu�uj� pou�it� filtru typu Cauer.

Pro n�vrh filtr� jsem pou�il n�vrhov� syst�m Syntfil (6), ve kter�m jsem rovn� provedl jednoduchou toleran�n� anal�zu. D�le jsem postupoval dle (4) a (7).

2.5.3.3. Toleran�n� sch�ma

Toleran�n� sch�ma doln� propusti vych�z� z v��e uveden�ch po�adavk� a je zobrazeno na obr. 2.7.

Obr. 2.7 : Toleran�n� sch�ma v�stupn�ch filtr�

Filtr by bylo mo�n� realizovat r�zn�mi aproximacemi. N�sleduj�c� tab. 2.3 uv�d� jejich seznam v�etn� v�sledn�ho stupn� filtru a nov� hodnoty as. Tato tabulka vych�z� z tabulky generovan� internetovou aplikac� Syntfil (6).

Tab. 2.3 : Srovn�n� aproximac�

|

aproximace |

stupe� |

nov� hodnota as (dB) |

|

Butterworth |

11 |

65.5 |

|

Chebyshev |

7 |

68.9 |

|

Inverzn� Chebyshev A |

7 |

68.9 |

|

Cauer A |

5 |

66.9 |

Vzhledem k velik�mu rozd�lu v ��dech filtr� jsem se nakonec rozhodl pro pou�it� aproximace Cauer A. V�sledn� zapojen� bude podstatn� jednodu��� ne� nap��klad v p��pad� aproximace Butterworth a t�m bude i m�n� n�chyln� na rozptyl hodnot pou�it�ch sou��stek.

Diferenci�ln� zesilova� p�izp�sobuje impedanci na 50 Ω. V�stupn� filtry budou tedy rovn� p�izp�sobeny na t�to impedanci se symetrick�m zakon�en�m.

V aplika�n�ch pozn�mk�ch firmy Analog Devices (5) jsou uvedeny praktick� testy n�kolika typ� filtr� s r�zn�m fyzick�m rozm�st�n�m jednotliv�ch sou��stek. Z t�chto test� vypl�v�, �e je v�hodn� rozd�lit ka�d� kondenz�tor, kter� je p�ipojen k zemi, na kombinaci dvou paraleln� zapojen�ch kondenz�tor� s polovi�n� hodnotou kapacity. Kondenz�tory takov�to dvojce pak budou um�st�ny �proti sob�.

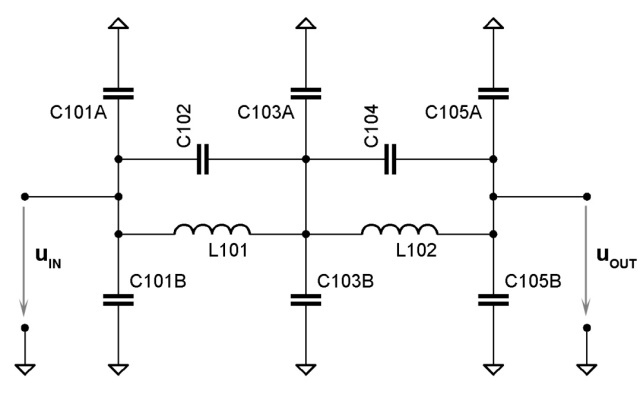

V�sledn� sch�ma v�stupn�ho filtru je na obr. 2.8. Zna�en� sou��stek obvod� p�ipojen�ch k prvn�mu v�stupu AD9958 pro p�ehlednost za��n� ��slem 101, k druh�mu pak 201.

Obr. 2.8 : V�stupn� filtr

Hodnoty sou��stek byly vypo�teny op�t internetovou aplikac� Syntfil (6) a jsou uvedeny v

Tab. 2.4 2.4. V t�to tabulce je rovn� uvedena pou�it� hodnota, respektive nejbli��� hodnota v �ad� nebo paraleln� kombinace dvou kondenz�tor�.

Tab. 2.4 : Hodnoty sou��stek pou�it�ch ve v�stupn�ch filtrech

|

sou��stka |

vypo�ten� hodnota |

pou�it� nomin�ln� hodnota |

|

C101 |

88.5 pF |

2x 47 pF |

|

C102 |

4.94 pF |

4,7 pF |

|

C103 |

152 pF |

2x 75 pF |

|

C104 |

9,19 pF |

8,2 pF |

|

C105 |

144 pF |

2x 75 pF |

|

L101 |

264 nH |

270 nH |

|

L102 |

272 nH |

270 nH |

Vypo�ten� hodnoty jsem p�epsal pou�it�mi nomin�ln�mi hodnotami a provedl anal�zu struktury. N�sleduj�c� graf (obr. 2.9) zobrazuje aproximaci a anal�zu LC filtru.

Obr. 2.9 : Aproximace a anal�za LC filtru

Anal�za LC filtru nepo��t� s rozptylem hodnot pou�it�ch sou��stek vlivem jejich tolerance.

2.5.4. V�stupn� rel�

P�i nastaven� nulov� v�stupn� frekvence se na v�stupech v�stupn�ch zesilova�� objev� stejnosm�rn� slo�ka, a proto jsem na v�stupy um�stil vysokofrekven�n� rel�, kter� p�i tomto nastaven� v�stup odpoj�. Rel� budou slou�it tak� k odpojen� v�stup� u�ivatelem.

Obr. 2.10 : V�stupn� rel� a jeho ��zen�

Na obr. 2.10 je uvedeno zapojen� v�stupn�ch rel� a jejich ��zen� pomoc� NPN tranzistoru v zapojen� se spole�n�m emitorem. RC filtr na b�zi tranzistoru zabra�uje pr�niku digit�ln�ho ru�en� do analogov� ��sti. Dioda D101 chr�n� tranzistor p�ed nap�ovou �pi�kou vzniklou p�i sp�n�n� induktivn� z�t�e.

2.5.5. Vstupy modulace

Vstupy integrovan�ho obvodu AD9958 P0, P1, P2 a P3 jsou ur�eny pro diskr�tn� modulaci frekvence, f�zov�ho posuvu a nebo amplitudy v�stupn�ho sign�lu. Diskr�tn� modulace p�esahuje rozsah t�to pr�ce, ale vzhledem k tomu, �e ji AD9958 umo��uje, rozhodl jsem se p�ipravit alespo� hardwarovou ��st tak, aby byla mo�n� jej� pozd�j�� programov� implementace.

Pro p�ipojen� extern�ch sign�l� diskr�tn� modulace je pou�it DIN konektor. K tomuto konektoru jsou p�ipojeny p�ep�ov� ochrany tvo�en� rezistory R1 a� R4 a diodami D1 a� D4 v�dy po dvou v jednom pouzd�e. N�sleduje neinvertuj�c� budi� 7407 (8), kter� zaji��uje spr�vn� rozpozn�n� vstupn�ch �rovn� odpov�daj�c�ch logick�m obvod�m TTL a proudov� pos�len� sign�lu. D�le jsou na v�stupech t�chto budi�� odporov� d�li�e nap�t� pro p�izp�soben� logick�ch �rovn�, kter� ji� ve sch�matu nejsou pro zjednodu�en� zakresleny. Sch�ma ��sti vstup� modulace je zobrazeno na obr. 2.11.

Obr. 2.11 : Vstupy pro diskr�tn� modulaci

2.5.6. Nap�jec� zdroje

Celkov� zapojen� nap�jec�ch zdroj� je na obr. 2.12.

2.5.6.1. Po�adovan� nap�jec� nap�t�

V cel�m zapojen� je pot�eba n�kolik n�sleduj�c�ch �rovn� nap�jec�ho nap�t�.

� +1,8 V pro analogovou ��st AD9958

� +1,8 V pro digit�ln� ��st AD9958

� +3,3 V pro ��d�c� ��st AD9958

� +5 V pro krystalov� oscil�tor a budi�e 7407

� +5 V pro digit�ln� ��st (mikrokontrol�r, LCD a Bluetooth modul)

� +9 V pro opera�n� zesilova�e

� -9 V pro opera�n� zesilova�e

2.5.6.2. Usm�r�ova�, filtra�n� kondenz�tory

Nap�jen� p��stroje jsem se rozhodl realizovat b�n� dostupn�m s�ov�m adapt�rem 9 V AC, 1 A. St��dav� nap�t� umo�n� snadn� vytvo�en� z�porn�ho nap�jec�ho nap�t� pro opera�n� zesilova�e. D�ky extern�mu adapt�ru nebude v p��stroji s�ov� nap�jec� nap�t�, co� zv��� v�slednou bezpe�nost.

Obr. 2.12 : Nap�jec� zdroje

Nap�jec� vstup jsem vy�e�il univerz�ln�, aby zde byla mo�nost p�ipojit i symetrick� nap�jec� nap�t�. V p��pad� p�ipojen� st��dav�ho nap�t� (nap��klad z v��e zm�n�n�ho s�ov�ho adapt�ru) se vstupy U+ a U- propoj�. Zna�en� sou��stek nap�jec� ��sti za��n� pro p�ehlednost ��slem 301. Na vstupu pro nap�jen� jsou zapojeny proudov� polymerov� vratn� pojistky (PolySwitch) PS301 a PS302. Za nimi n�sleduje jednocestn� usm�rn�n� dv�ma diodami D301 a D302 a filtra�n� kapacity C301, C302 a C303. Diody jsem volil b�n� usm�r�uj�c� s dostate�n� velik�m IFAV, konkr�tn� typ 1N4007. Kapacitu filtra�n�ch kondenz�tor� jsem stanovil n�sledovn�:

Nap�t� na filtra�n�ch kondenz�torech kladn� nap�jec� v�tv� bude bez z�t�e:

|

|

(2.16) |

Integrovan� stabiliz�tory 7809 (7909) pot�ebuj� pro svou spr�vnou funkci �bytek nap�t� mezi vstupem a v�stupem alespo� 2 V. Pot�ebuj� na sv�m vstupu tedy alespo� 9 + 2 = 11 V (-11 V).

Nap�t� na filtra�n�ch kondenz�torech by tedy ani p�i maxim�ln�m mo�n�m proudov�m zat�en� nem�lo klesnout pod 11 V. Z toho vypl�v� maxim�ln� mo�n� zvln�n� v procentech:

|

|

(2.17) |

Maxim�ln� proudov� odb�r z kladn� nap�jec� v�tve p�edpokl�d�m s rezervou Im+ = 250 mA, ze z�porn� p�ibli�n� Im- = 100 mA.

Kapacity filtra�n�ch kondenz�tor� jsem stanovil dle n�sleduj�c�ho vztahu:

|

|

(2.18) |

|

|

(2.19) |

Vzhledem k toleranci b�n�ch elektrolytick�ch kondenz�tor� �20 %, jejich mo�n�mu poklesu kapacity a toleranci s�ov�ho nap�t� je vhodn� volit kapacitu je�t� o n�kolik des�tek procent vy���. Pro kladnou nap�jec� v�tev jsem tedy zvolil CF+ = 2 mF a pro z�pornou nap�jec� v�tev CF- = 1 mF. Kapacita CF+ je realizov�na paraleln� kombinac� kondenz�tor� C301 a C302. Kapacita CF- pak kondenz�torem C303.

2.5.6.3. Stabiliz�tory

Nejprve jsem cht�l realizovat v�echna nap�jec� nap�t� t��-v�vodov�mi stabiliz�tory s pevn�m v�stupn�m nap�t�m. Stabiliz�tory s v�stupn�m nap�t�m +1,8 V a 3,3 V se sice b�n� vyr�b�j�, ale jsou obt�n� dostupn�. Proto jsem se rozhodl pro pou�it� b�n� dostupn�ho regulovateln�ho stabiliz�toru nap�t� LM317 (9). Zde je zapojen v nejjednodu���m mo�n�m zapojen�. Vzhledem k tomu, �e na v�stupu LM317 nebudou p�ipojeny ��dn� velik� kapacitn� z�t�e, nen� t�eba pou��vat extern� ochrann� diody. Rezistory R301 a R302 u stabiliz�toru IC304 ur�uj� jeho v�stupn� nap�t�, kter� m� b�t 1,8 V. P�i ur�en� hodnot odpor� t�chto rezistor� jsem pou�il vzorec uveden� v katalogov�ch listech obvodu LM317 (9).

|

|

(2.20) |

www.elweb.cz

Proud tekouc� v�vodem adj (Iadj ) lze zanedbat. Doporu�en� hodnota odporu rezistoru R301 je 240 Ω. Pou�il jsem tedy tuto hodnotu. Odpor rezistoru R302 jsem pak vypo�etl z v��e uveden�ho vztahu.

|

|

(2.21) |

Z �ady hodnot E24 jsem pak vybral nejbli��� ni��� hodnotu: R302 = 100 Ω.

V�po�et hodnot odpor� rezistor� p��slu�ej�c�ch ke stabiliz�tor�m IC307 je shodn�: R305 = R301 = 240 Ω, R306 = R302 = 100 Ω.

Odpory rezistor� p��slu�ej�c�ch ke stabiliz�toru IC303 s v�stupn�m nap�t�m 3,3 V jsou n�sleduj�c�:

R303 = R301 = 240 Ω

|

|

(2.22) |

Z �ady hodnot E24 jsem pak vybral nejbli��� ni��� hodnotu: R304 = 390 Ω.

2.6.1. ��d�c� mikrokontrol�r

P�i v�b�ru vhodn�ho ��d�c�ho mikrokontrol�ru jsem zohlednil p�edev��m sv� dosavadn� zku�enosti s produkty firmy Microchip. Pro tuto aplikaci bude zcela jist� posta�ovat osmibitov�. Budu tedy vyb�rat z �ad PIC16F a PIC18F.

N�sleduj�c� tab. 2.5 uv�d� seznam sou��st� propojen�ch s mikrokontrol�rem a po�et pin�, respektive dr�t�, kter�mi by m�ly b�t tyto sou��sti propojeny.

Tab. 2.5 : Seznam sou��st� propojen�ch s mikrokontrol�rem

|

sou��st |

po�et pin� |

|

AD9958 |

6 |

|

v�stupn� rel� |

2 |

|

LCD displej |

11 |

|

kl�vesnice |

8 |

|

Bluetooth modul |

4 |

|

celkem pin�: |

31 |

Celkov� pot�ebn� po�et vstupn�-v�stupn�ch pin� mikrokontrol�ru je tedy 31. Volil jsem tedy mezi 40-ti pinov�mi mikrokontrol�ry, kter� maj� 33 takov�chto pin�. Nakonec jsem se rozhodl pro PIC16F877 (10), kter� se mi jev� jako optim�ln�. Tyto mikrokontrol�ry maj� velmi dobrou vz�jemnou kompatibilitu, tak�e jej bude mo�n� v p��pad� budouc� pot�eby snadno vym�nit bez �pravy hardware.

Hodinov� sign�l pro mikrokontrol�r tvo�� 20 MHz extern� krystal. Programov�n� bude prob�hat p��mo v aplikaci p�es rozhran� ICSP. N�sleduj�c� tab. 2.6 uv�d� zapojen� v�ech v�vod� mikrokontrol�ru v t�to aplikaci.

Celkov� sch�ma digit�ln� ��sti je uvedeno v p��loze.

Tab. 2.6 : Zapojen� pin� mikrokontrol�ru

|

��slo pinu |

jm�no pinu |

zapojen� |

|

1 |

MCLR/VPP |

pull-up rezistor, ICSP |

|

2 |

PA0/AN0 |

rel�, 1. v�stup |

|

3 |

PA1/AN1 |

rel�, 2. v�stup |

|

4 |

PA2/AN2/VREF-/CVREF |

AD9958, CS |

|

5 |

PA3/AN3/VREF+ |

AD9958, IO_UPDATE |

|

6 |

PA4/T0CKI/C1OUT |

- |

|

7 |

PA5/AN4/SS/C2OUT |

AD9958, RESET |

|

8 |

PE0/RD/AN5 |

AD9958, SDIO_0 |

|

9 |

PE1/WR/AN6 |

AD9958, SDIO_1 |

|

10 |

PE2/CS/AN7 |

AD9958, SCLK |

|

11 |

VDD |

nap�jec� nap�t� +5 V |

|

12 |

VSS |

GND |

|

13 |

OSC1/CLKI |

extern� krystal |

|

14 |

OSC2/CLKO |

extern� krystal |

|

15 |

PC0/T1OSO/T1CKI |

LCD, D2 |

|

16 |

PC1/T1OSI/CCP2 |

LCD, D1 |

|

17 |

PC2/CCP1 |

LCD, D0 |

|

18 |

PC3/SCK/SCL |

- |

|

19 |

PD0/PSP0 |

Bluetooth, RTS |

|

20 |

PD1/PSP1 |

Bluetooth, CTS |

|

21 |

PD2/PSP2 |

LCD, D3 |

|

22 |

PD3/PSP3 |

LCD, D4 |

|

23 |

PC4/SDI/SDA |

LCD, D5 |

|

24 |

PC5/SDO |

LCD, D6 |

|

25 |

PC6/TX/CK |

Bluetooth, RXD |

|

26 |

PC7/RX/DT |

Bluetooth, TXD |

|

27 |

PD4/PSP4 |

LCD, D7 |

|

28 |

PD5/PSP5 |

LCD, E |

|

29 |

PD6/PSP6 |

LCD, R/W |

|

30 |

PD7/PSP7 |

LCD, R/S |

|

31 |

VSS |

GND |

|

32 |

VDD |

nap�jec� nap�t� +5 V |

|

33 |

PB0/INT |

kl�vesnice |

|

34 |

PB1 |

kl�vesnice |

|

35 |

PB2 |

kl�vesnice |

|

36 |

PB3/PGM |

kl�vesnice |

|

37 |

PB4 |

kl�vesnice |

|

38 |

PB5 |

kl�vesnice |

|

39 |

PB6/PGC |

kl�vesnice, ICSP |

|

40 |

PB7/PGD |

kl�vesnice, ICSP |

Kl�vesnice je p�ipojena na porty B, proto�e PIC16F877 umo��uje generov�n� p�eru�en� p�i zm�n� logick� �rovn� pr�v� na pinech PB,3 a� PB,7. Toho lze vyu��t pro snadn� zji�t�n� stisku tla��tka. PIC16F877 rovn� obsahuje integrovan� rozhran� USART, ke kter�mu bude p�es porty PC,6 a PC,7 p�ipojen Bluetooth modul.

Ostatn� piny jsou vz�jemn� z�m�nn� a jejich propojen� s ostatn�mi sou��stmi jsem p�izp�sobil rozm�st�n� sou��stek na desce plo�n�ch spoj�, respektive co nejjednodu���mu n�vrhu t�to desky.

2.6.2. LCD displej

LCD displej jsem zvolil takov�, aby na n�m mohly b�t p�ehledn� zobrazeny v�echny pot�ebn� informace. Z obr. 2.13 je patrn�, �e posta�� textov� displej 2x 16 znak�. LCD displej je ��zen standardn�m obvodem HD44780 (11).

|

3 |

9 |

|

9 |

9 |

9 |

|

9 |

9 |

9 |

|

H |

z |

|

|

|

|

3 |

5 |

9 |

� |

|

2 |

, |

5 |

5 |

V |

|

2 |

, |

5 |

5 |

V |

Obr. 2.13 : P��klad zobrazen� informac� na LCD displeji

Proveden� displeje jsem zvolil modr� inverzn� s b�l�m podsv�cen�m, kter� je l�pe �iteln� ne� b�n� �edozelen�.

2.6.3. Kl�vesnice

K ovl�d�n� p��stroje bude slou�it numerick� kl�vesnice. Vzhledem k omezen�mu po�tu pin� mikrokontrol�ru bude vhodn� pou��t maticovou kl�vesnici. Takov�to kl�vesnice se b�n� vyr�b�j� 12-ti tla��tkov� (3x4) a 16-ti tla��tkov� (4x4). Krom� ��sel pro zad�v�n� hodnot je pot�eba n�kolik dal��ch tla��tek pro volbu, kter� z parametr� v�stupn�ch sign�l� m� b�t pr�v� editov�n, p��padn� i pro dal�� funkce. Proto jsem nakonec zvolil druh� z v��e uveden�ch typ�, tedy 16-ti tla��tkovou maticovou kl�vesnici, konkr�tn� 16KEY od firmy Velleman.

2.6.4. Bluetooth

P��stroj bude mo�n� v budoucnu ovl�dat prost�ednictv�m bezdr�tov�ho rozhran� Bluetooth z osobn�ho po��ta�e, notebooku nebo PDA. Pro tento ��el jsem pou�il pr�myslov� Bluetooth modul OEMSPA_311 firmy ConnectBlue (12).

Sch�ma

www.elweb.cz

Jak ji� bylo uvedeno v��e, za��zen� je rozd�leno na dv� ��sti � analogovou a digit�ln�. Tyto ��sti budou realizov�ny na dvou samostatn�ch desk�ch plo�n�ch spoj�.

Ob� desky jsem navrhoval v programu CadSoft Eagle verze 4.16. Postupoval jsem dle pravidel a princip� n�vrhu uveden�ch v (13). Pro tuto aplikaci je nezbytn� pou�it� rozlit� m�d�n� plochy vodiv� spojen� se zem�. Proto jsou ob� desky realizov�ny jako dvojstrann� s prokovy.

Ob� desky jsou vz�jemn� propojeny ploch�m kabelem upevn�n�m do samo�ezn�ch konektor� ur�en�ch pro p��m� osazen�.

3.1.1. Digit�ln� ��st

Desku plo�n�ch spoj� digit�ln� ��sti jsem se rozhodl um�stit p��mo pod LCD displej, aby tyto dva d�ly nemusely b�t propojeny ploch�m kabelem, ale p��mo konektorem. Ploch� kabely maj� toti� b�n� polovi�n� rozte� (1,27 mm) oproti rozte�i v�vod� LCD displeje (2,54 mm), co� by konstrukci zbyte�n� komplikovalo.

Vzhledem k um�st�n� desky plo�n�ch spoj� digit�ln� ��sti p��mo pod LCD displejem a i d�ky pom�rn� mal�mu po�tu sou��stek, kter� obsahuje, jsem zvolil rozm�ry t�to desky shodn� s rozm�ry modulu LCD displeje.

Mikrokontrol�r jsem pou�il z d�vod� mo�nosti um�st�n� do patice (a t�m i snadn� v�m�n�) v �irok�m pouzdru PDIP40.

P�i n�vrhu desky jsem vyu��val mo�nosti z�m�ny vstupn�-v�stupn�ch pin� mikrokontrol�ru v jeho programu. T�m se nejen n�vrh, ale p�edev��m i v�sledn� deska zna�n� zjednodu�ily.

Pr�myslov� Bluetooth modul je um�st�n na okraji desky tak, aby se p�ed jeho integrovanou ant�nou nenach�zely ��dn� spoje ani elektronick� sou��stky.

3.1.2. Analogov� ��st

Druhou desku plo�n�ch spoj� v t�to pr�ci naz�v�m jako �analogov� ��st�, p�esto�e je tvo�ena nejen analogov�mi, ale analogov�-digit�ln�mi a digit�ln�mi obvody. Ob� dv� strany t�to desky jsou pokryty rozlitou zem� (m�d�nou plochou vodiv� spojenou se zem�). Sign�lov� spoje jsou vedeny prakticky jen ze strany spoj� tak, aby rozlit� zem ze strany sou��stek nebyla p��li� p�eru�ov�na. Deska je d�le rozd�lena na digit�ln� a analogovou ��st a tyto dv� ��sti jsou odd�leny tzv. izola�n�m p��kopem. Tento izola�n� p��kop je p�emost�n spoji jen v t�sn� bl�zkosti integrovan�ho obvodu p��m� digit�ln� synt�zy. To plat� i pro propojen� digit�ln� a analogov� zem�. Rozlit� zem je mezi ob�ma stranami desky propojov�na pomoc� prokov�. Po obvodu cel� desky je z obou stran jen rozlit� zem kv�li omezen� vyza�ov�n� a indukci ru�en�.

Sign�lov� cesty obou v�stup� DDS jsou vedeny tak, aby jejich celkov� d�lka od integrovan�ho obvodu AD9958 a� po v�stupn� konektory byla shodn�.

P�i rozm�st�n� sou��stek v�stupn�ch filtr� jsem postupoval p�edev��m dle aplika�n�ch pozn�mek Analog Devices (5). C�vky jsou navz�jem pooto�eny o 90� tak, aby byla minimalizov�na jejich vz�jemn� indukce. Pou�il jsem speci�ln� vzduchov� proveden� ur�en� pro vysokofrekven�n� techniku v pouzdru SMD velikosti 0805. V�echny kondenz�tory ve v�stupn�ch filtrech, kter� jsou p�ipojeny k zemi, jsou rozd�leny na kombinaci dvou paraleln� zapojen�ch kondenz�tor� s polovi�n� hodnotou kapacity. Kondenz�tory takov�to dvojice jsou pak um�st�ny �proti sob�.

Po cel� desce je um�st�no mno�stv� keramick�ch kondenz�tor� o hodnot� 47 nF pro blokaci nap�jec�ch nap�t�.

V�t�ina pou�it�ch sou��stek je v proveden� pro povrchovou mont� (SMD). V�echny sou��stky v�etn� zbyl�ch THT sou��stek jsou osazeny pouze z jedn� strany desky plo�n�ch spoj�.

Program mikrokontrol�ru jsem vytvo�il v assembleru ve v�vojov�m prost�ed� MPLAB IDE firmy Microchip. Program obsahuje celkov� p�ibli�n� 2500 instrukc�.

3.2.1. LCD a kl�vesnice

��zen� LCD displeje prob�h� paraleln� a jednosm�rn�. V�em dvaat�iceti znak�m displeje odpov�d� 32 pam�ov�ch registr� RAM v mikrokontrol�ru. Znaky jsou tedy upravov�ny nejprve v RAM a n�sledn� jsou p�ekresleny na LCD displej v�echny sou�asn�.

�estn�cti-tla��tkov� kl�vesnice je p�ipojena maticov�. Na v�echny jej� ��dky je nejprve nastavena logick� 1. Sign�ly ze sloupc� jsou p�ipojeny na porty PB,4 a� PB,7 a p�i stisku libovoln�ho tla��tka generuj� p�eru�en� b�hu programu mikrokontrol�ru. P�i p�eru�en� je pomoc� zm�n logick�ch �rovn�ch na portech PB,0 a� PB,3 p�ipojen�ch na ��dky maticov� kl�vesnice zji�t�no, kter� tla��tko bylo stisknuto.

3.2.2. ��zen� AD9958

Mikrokontrol�r ��d� integrovan� obvod p��m� digit�ln� synt�zy prost�ednictv�m s�riov� sb�rnice, nastavuje tedy p�edev��m delta registr v obvodu AD9958 na hodnotu odpov�daj�c� nastaven� v�stupn� frekvenci, d�le tak� registry ��d�c� relativn� f�zov� posuv a amplitudu obou kan�l�. Hodnota v�stupn� frekvence je naps�na na LCD pomoc� numerick� kl�vesnice. Sedmi dekadick�m ��slic�m zobrazen�m na LCD displeji, odpov�d� sedm registr� pam�ti RAM v mikrokontrol�ru. Tyto ��slice reprezentuj� hodnotu v�stupn� frekvence v Hz. Program se po ka�d� zm�n� tohoto ��sla postar� o skryt� bezv�znamn�ch nul. P�i ka�d� zm�n� program rovn� p�evede ��slo z dekadick� soustavy do soustavy dvojkov� a uprav� jej. Pak toto ��slo ve dvojkov� soustav� ulo�� po s�riov�m veden� do obvodu AD9958. ��zen� amplitud obou sign�l� a vz�jemn�ho f�zov�ho posuvu prob�h� obdobn�m zp�sobem.

Amplituda v�stupn�ch sign�l� je nastavov�na p��mo v AD9958 digit�ln�, tedy je�t� p�ed D/A p�evodn�ky. Jistou dan� za takto jednoduch� �e�en� je to, �e p�i nastaven� men��ch amplitud dojde ke zhor�en� spektr�ln� �istoty v�stupn�ho sign�lu. Tento probl�m by bylo mo�n� eliminovat pou�it�m p�ep�nateln�ch atenu�tor�.

3.2.3. Bluetooth

Pr�myslov� Bluetooth modul je p�ipojen na USART rozhran� mikrokontrol�ru. Jak�koli p�ij�man� data prost�ednictv�m Bluetooth vyvolaj� p�eru�en� v b�hu programu mikrokontrol�ru. Ten je pak po autorizaci bezdr�tov�ho za��zen� (PC, PDA, mobiln� telefon...) p�ipraven pro p��jem dat. Data maj� velmi jednoduch� form�t. P�en�� se pouze informace o v�stupn� frekvenci, f�zov�m posuvu a amplitud�ch v�stupn�ch sign�l�.

V�e jsem navrhoval tak, aby bylo mo�n� sestaven� gener�tor snadno vestav�t do p��strojov� krabice. Pou�il jsem plechovou hlin�kovou krabici firmy Boss, kterou jsem nechal zak�zkov� upravit. Jednalo se p�edev��m o vy��znut� otvor� v �eln�m panelu CNC fr�zou a vytvo�en� grav�rovan�ch popisk�.

Obr. 3.1 : Rozm�st�n� otvor� v �eln�m panelu

Na obr. 3.1 je vid�t rozm�st�n� otvor� v �eln�m panelu. Vlevo je um�st�n hlavn� vyp�na�. Uprost�ed pak LCD displej a pod n�m oba v�stupn� BNC konektory a vstupn� konektor pro extern� diskr�tn� modulaci. V prav� ��sti �eln�ho panelu je um�st�na numerick� kl�vesnice.

Na obr. 3.2 je fotografie s popisem hlavn�ch ��st� obou osazen�ch desek plo�n�ch spoj� um�st�n�ch do p��strojov� krabice.

Obr. 3.2 : Osazen� desky plo�n�ch spoj�

Na obr. 3.3 je fotografie �eln�ho panelu hotov�ho p��stroje.

Obr. 3.3 : �eln� panel hotov�ho p��stroje

Ovl�d�n� je velmi jednoduch� a intuitivn�. U�ivatel pouze jedn�m ze �ty� tla��tek v prav� ��sti kl�vesnice (f, φ,Um1,Um2) zvol�, kter� hodnota m� b�t editov�na a n�sledn� na numerick� kl�vesnici nap�e hodnotu. M�nit lze frekvence, f�zov� posuv a zvl amplitudy obou v�stupn�ch sign�l�. V�stupn� sign�l se m�n� ji� v pr�b�hu zad�v�n� hodnoty a zadanou hodnotu nen� pot�eba nijak potvrzovat.

P�i m��en� v�stupn�ch sign�l� gener�toru jsem pou�il n�sleduj�c� p��stroje:

- Spektr�ln� analyz�tor (Rohde & Schwarz FSP Spectrum Analyzer 9 kHz � 3 GHz)

- Osciloskop (Agilent Technologies DSO 6032A 300 MHz)

- Osciloskop (Metrix OX803B 40 MHz)

- Multimetr (Metex P-10)

Pomoc� v��e uveden�ho spektr�ln�ho analyz�toru jsem zm��il �rovn� v�konu prvn�ch p�ti harmonick�ch slo�ek v�stupn�ho sign�lu pro frekvenci 100 kHz a pak od 2 MHz do 40 MHz s krokem 2 MHz. Nam��en� v�sledky jsou zobrazeny v podob� grafu na obr. 4.1.

Obr. 4.1 : �rovn� v�stupn�ho v�konu harmonick�ch slo�ek

Z grafu je vid�t pokles v�konu 1. harmonick� slo�ky na vy���ch frekvenc�ch a rovn� pom�rn� v�razn� druh� a t�et� harmonick� slo�ka.

P�i vy���ch v�stupn�ch frekvenc�ch (p�ibli�n� od 28 MHz) byly ve frekven�n�m spektru p�i m��en� patrn� dal�� ne��douc� spektr�ln� ��ry, kter� nejsou zahrnuty na obr. 4.1. Jedn� se o vy��� harmonick� slo�ky od generovan� frekvence p�enesen� do z�kladn�ho p�sma, p�i�em� n�kter� z nich nelze potla�it v�stupn�mi filtry. P��klad takov�to situace je patrn� na obr. 4.2.

Obr. 4.2 : V�sledek m��en� spektr�ln�m analyz�torem p�i v�stupn� frekvenci 40,2 MHz

Prvn� zna�kou (marker) je ozna�ena 1. harmonick� na frekvenci f1 = 40,2 MHz. Vy��� harmonick� frekvence (80,4 MHz; 120,6 MHz atd.) budou sice nad mezn� frekvenc� v�stupn�ho filtru a tud� potla�eny, ale ve frekven�n�m spektru se objev� jako p�enesen� do z�kladn�ho p�sma. Dle teoretick�ch v�po�t� by se m�la v z�kladn�m p�smu objevit druh� harmonick� slo�ka na frekvenci:

|

|

(4.1) |

www.elweb.cz

Tato frekvence je tak� relativn� daleko za mezn�m kmito�tem v�stupn�ho filtru a proto na obr. 4.2 nen� patrn�. T�et� harmonick� se do z�kladn�ho p�sma p�esune na frekvenci:

|

|

(4.2) |

Tato frekvence je ji� v propustn�m p�smu v�stupn�ho filtru, na obr. 4.2 se zobrazila a je ozna�ena druhou zna�kou (marker). P�esto�e jej� vypo�ten� p�edpokl�dan� frekvence byla 13,6 MHz, byla nam��ena na frekvenci 40,2 � 27,4 = 12,8 MHz. Je to z�ejm� zp�sobeno chybou m��en� vzniklou nastaven�m p��li� velk�ho frekven�n�ho rozsahu (SPAN) na spektr�ln�m analyz�toru. D�ky tomu je ale v�ak vid�t, �e jsou dal�� nep�enesen� vy��� harmonick� spolehliv� potla�eny v�stupn�m filtrem.

Obdobn� situace nast�v� p�i v�stupn� frekvenci f1 = 30 MHz. Toto m��en� je na obr. 4.3. Zde jsou vid�t krom� prvn� harmonick� i dal�� dv� p�enesen� vy��� harmonick� slo�ky, konkr�tn� t�et� na frekvenci 42,6 MHz a �tvrt� na frekvenci 17,4 MHz. V tomto p��pad� lze op�t analogicky spo��tat teoretick� hodnoty frekvence p�enesen� t�et� harmonick� slo�ky:

|

|

(4.3) |

a teoretickou hodnotu frekvence p�enesen� �tvrt� harmonick�:

|

|

(4.4) |

I zde jsou patrn� jist� rozd�ly mezi teoretick�mi v�po�ty a nam��en�mi v�sledky.

Obr. 4.3 : V�sledek m��en� spektr�ln�m analyz�torem p�i v�stupn� frekvenci 30 MHz

Zaj�mav� je z hlediska principu a vlastnost� p��m� digit�ln� synt�zy nastaven� v�stupn� frekvence do t�sn� bl�zkosti Nyqustova krit�ria tedy do bl�zkosti poloviny vzorkovac� frekvence. P�esto�e je gener�tor navr�en pro maxim�ln� v�stupn� frekvenci 40 MHz, upravil jsem program mikrokontrol�ru pro ��ely m��en� tak, aby bylo mo�n� nastavit v�stupn� frekvenci i vy���.

Nastavil jsem tedy v�stupn� frekvenci 60 MHz a provedl dal�� m��en� zobrazen� na obr. 4.4. Prvn� harmonick� slo�ka se nach�z� ji� za mezn� frekvenc� v�stupn�ho filtru a je tedy zna�n� utlumena � p�ibli�n� o 30 dB. Zde stoj� za zm�n�n� srovn�n� praktick�ho m��en� s anal�zou v�stupn�ho filtru z obr. 2.9, kde �tlum na frekvenci 60 MHz vych�z� rovn� p�ibli�n� 30 dB.

Obr. 4.4 : V�sledek m��en� spektr�ln�m analyz�torem p�i v�stupn� frekvenci 60 MHz

D�le je zde vid�t hned n�kolik ne��douc�ch harmonick�ch slo�ek. Druhou zna�kou (marker) je ozna�ena p�enesen� t�et� harmonick� na frekvenci:

|

|

(4.5) |

Jedn� se o re�ln� sign�l, a proto je frekven�n� spektrum symetrick� dle svisl� osy. Z toho vypl�v� pou�it� absolutn�ch hodnot ve v��e uveden�m vztahu (4.5). Tato teoretick� hodnota p�esn� odpov�d� hodnot� nam��en� (60 - 14,2 = 45,8 MHz).

T�et� zna�ka (marker) p��slu�� obrazu na frekvenci:

|

|

(4.6) |

Op�t se vypo�ten� hodnota shoduje s nam��enou frekvenc� (60 + 14,2 = 74,2 MHz)

Pod �tvrtou zna�kou je p�enesen� druh� harmonick� slo�ka na frekvenci:

|

|

(4.7) |

Nam��ena byla na frekvenci t�m�� shodn� (60 � 46 = 14 MHz).

D�le bylo provedeno m��en� vz�jemn�ho chybov�ho f�zov�ho posuvu obou kan�l� p�i nastaven�m nulov�m vz�jemn�m f�zov�m posuvu. K tomuto m��en� byl pou�it v��e uveden� digit�ln� osciloskop. V�sledky m��en� jsou zobrazeny v podob� grafu na obr. 4.5.

V dob� m��en� prob�hal experiment s v�stupn�mi filtry a hodnoty kondenz�tor� C102 a C104 (viz obr. 2.8) byly u prvn�ho a druh�ho kan�lu odli�n�, co� toto m��en� bohu�el znehodnocuje. Je velmi pravd�podobn�, �e by bylo p�i pou�it� shodn�ch filtr� dosa�eno podstatn� lep��ch v�sledk�. M��en� jsem z �asov�ch d�vod� ji� nemohl opakovat. I tak byl nam��en� f�zov� posuv a� do frekvence 1 MHz men�� ne� 1�.

Obr. 4.5 : V�sledky m��en� chybov�ho f�zov�ho posuvu

Poda�ilo se navrhnout a vytvo�it plnohodnotn� laboratorn� p��stroj, kter� lze pou��vat jako zdroj testovac�ho sign�lu p�i mnoha laboratorn�ch m��en�ch. Jeho v�jime�nost oproti b�n� pou��van�m gener�tor�m spo��v� v mo�nosti nastaven� vz�jemn�ho f�zov�ho posuvu dvou v�stupn�ch harmonick�ch sign�l�. P��stroj je p�ipraven pro programovou implementaci diskr�tn� modulace f�ze, frekvence i amplitudy extern�m sign�lem a tak� pro bezdr�tov� ovl�d�n� prost�ednictv�m pr�myslov�ho Bluetooth.

V pr�b�hu pr�ce jsem se podrobn�ji sezn�mil

s mnoha obory analogov�, analogov�-digit�ln� i digit�ln� techniky. Prakticky

jsem aplikoval n�vrhy obvodov�ch �e�en� jednotliv�ch celk�, jako jsou nap�jec�

zdroje, LC filtry, zesilova�e, obvody mikrokontrol�rov� techniky a pevn� logiky

a dal��. Navrhl jsem desky plo�n�ch spoj� i celkovou realizaci fin�ln�ho

produktu, kter� jsem n�sledn� �sp�n� sestavil.

V�sledky m��en� prok�zaly, �e je navr�en� a sestaven� gener�tor pln� funk�n� v cel�m pracovn�m rozsahu. V�stupn� frekvenci lze nastavit v rozsahu 1 Hz a� 40 MHz s krokem 1 Hz, vz�jemn� f�zov� posuv v rozsahu 0 a� 359� s krokem 1� a amplitudy v�stupn�ch sign�l� v rozsahu 0 V a� 2,55 V s krokem 0,01 V. Odstup (nep�enesen�ch) vy���ch harmonick�ch slo�ek byl v cel�m frekven�n�m rozsahu lep�� ne� 45 dB. Vzhledem k parametr�m pou�it�ch sou��stek a dodr�en� nejen pravidel a princip� n�vrhu, ale i mnoha doporu�en� v�robc�, jsem o�ek�val minim�ln� o deset dB lep�� spektr�ln� �istotu v�stupn�ho sign�lu. Pro jej� zlep�en� by bylo pot�eba opakovat m��en� jednotliv�ch blok� gener�toru, dohledat nejslab�� �l�nek a prov�st jeho optimalizaci a p��padn� i zv��it rozd�l hodinov� a maxim�ln� generovan� frekvence. Pokles amplitudy v�stupn�ho sign�lu p�i vy���ch frekvenc�ch a rovn� f�zov� posuv v�stupn�ch filtr� by bylo mo�n� d�le kompenzovat programov� korek�n� tabulkou.

1. Skalick�, P. ��slicov�

syst�my v radiotechnice. 1. vyd�n�. Praha : Vydavatelstv� �VUT, 2004.

ISBN 80-01-02854-2.

2. Analog Devices,

Inc. AD9958 2-Channel 500 MSPS DDS with 10-Bit DACs. Analog Devices. [Online]

2005. http://www.analog.com.

3. Texas Instruments

Incorporated. THS3091 High Voltage Low Distortion Current-Feedback OP Amps

(Rev. F). TI. [Online] 2003-2007.

4. H�jek, K.,

Sedl�k, J. Kmito�tov� filtry. Praha : BEN - technick�

literatura, 2002. ISBN 80-7300-023-7.

5. Brandon, D. a

Gentile, K. AN-837 APPLICATION NOTE DDS-Based Clock Jitter Performance vs.

DAC Reconstruction Filter Performance. Analog Devices. [Online] 2006.

http://www.analog.com.

6. Kobliha, O.,

Hospodka, J. a Bi��k, J. Synt�za elektrick�ch filtr�. Syntfil. [Online]

2004. https://obvody.feld.cvut.cz/syntfil.

7. Dav�dek, V.,

Laipert, M., Vl�ek, M. Analogov� a ��slicov� filtry. Praha :

�VUT, 2006. ISBN 80-01-03026-1.

8. National

Semiconductor Corporation. DM5407/DM7407 Hex Buffers with High Voltage

Open-Collector Outputs. National. [Online] 1995.

http://www.national.com.

9. �.

LM117/LM317A/LM317 3-Terminal Adjustable Regulator. National. [Online]

2007. http://www.national.com.

10. Microchip

Technology Inc. PIC16F87XA Data Sheet 28/40/44-Pin Enhanced Flash

Microcontrollers. Microchip. [Online] 2003. http://www.microchip.com.

11. Hitachi.

HD44780U (LCD-II) Dot Matrix Liquid Crystal Display Controller/Driver. [Online]

1999. http://www.lcd-module.de/.

12. connectBlue AB.

INDUSTRIAL BLUETOOTH OEM Serial Port Adapter cB-0901 Electrical &

Mechanical Datasheet. 2007.

13. Z�hlava, V. N�vrh

a konstrukce desek plo�n�ch spoj�. Praha : Nakladatelstv� �VUT, 2005.

IBSN 80-01-03351-1.

14. SEIKO EPSON

CORP. PROGRAMMABLE HIGH-FREQUENCY CRYSTAL OSCILLATOR SG-8002JC series. Spezial.

[Online] 2007. http://www.spezial.cz.

15. MEDER

electronic. Miniature Reed Relays for High Frequency Switching - LP Series.

[Online] 2007. http://www.meder.cz.

16. W�rth Elektronik

eiSos GmbH & Co. KG. Ceramic-SMD-Inductor WE-KI 744760227C. W�rth

Elektronik. [Online] 2006. http://www.we-online.com.

17. Val�ch, D.

Riadenie priameho ��slicov�ho syntez�tora AD pomocou PC. [Online] 1999.

http://www.balu.sk/skola/riadenie_DDS.pdf.

18. Pun�och��, J.

Opera�n� zesilova�e v elektronice. Praha : BEN - technick�

literatura, 2002. ISBN 80-7300-059-8.

19. Hrab��ek, J.

Komunikace mikrokontrol�ru s okol�m 2. Praha : BEN - technick�

literatura, 2000. ISBN 80-86056-73-2.

20. Krej�i��k, A.

Line�rn� nap�jec� zdroje. Praha : BEN - technick� literatura, 2001.

ISBN 80-7300-002-4.

21. Proke�, A. a

�erm�k, K. Vyu�it� p��m� kmito�tov� synt�zy v radiotechnice. Elektrorevue

: �asopis pro elektroniku. [Online] 2003. http://www.elektrorevue.cz.

22. �tokr, M. Principy

p��m� digit�ln� synt�zy. Slaboproud� obzor. P��loha (nejen) pro mlad� in�en�ry.

Praha : �eskoslovensk� sekce IEEE.

23. Vacek, V. U�ebnice

programov�n� PIC. Praha : BEN - technick� literatura, 2000. ISBN

80-86056-87-2.

24. L�n��ek, R. Elektronika,

obvody, sou��stky a d�je. Praha : BEN - technick� literatura, 1998.

ISBN 80-86056-25-2.

www.elweb.cz

obr�zek/sch�ma ve form�tu gif

fotografie/obr�zek ve form�tu jpg

| << p�edchoz� �l�nek 0405miniaturn� dvojit� zdroj nap�t� 2x 1,3 a� 10V, 2x0,5A s LED voltmetry | dal�� �l�nek >> 0103Digit�ln� ��zen� P�EDZESILOVA� s LCD displejem (3 vstupy, korekce, roz���en� sterea...) |